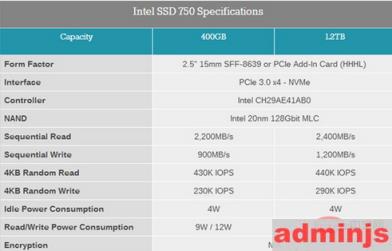

PCIe3.0x4理论最大读写速度为4GB/s,不管协议成本如何,每秒可以传输4GB/4K大小的IO,值为1M,即理论上最大IOPS为1000K。因此,无论SSD底部使用什么介质,flash还是3d xpoint,接口速度就这样,最大IOPS是不可能超过这个值的。

PCIE接口介绍

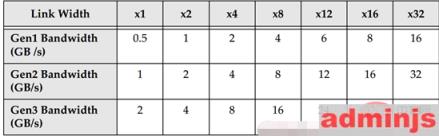

PCIE发展到现在,速度一代比一代快。

Link Width这一行,我们看到X1、X2、X4…这是什么意思?这是指PCIE连接的通道数(Lane)。就像高速公路一样,有一条道路,两条道路,四条道路,但八条道路或更多道路并不常见,但PCIE最多可以有32条道路。

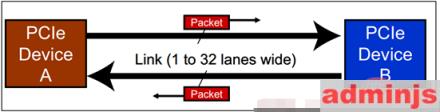

两个设备之间的PCIE连接,称为Link,如下图所示:

从A到B,是双向连接,汽车可以从A到B,同时,汽车也可以从B到A,各行其道。在两个PCIE设备之间,有一个特殊的发送和接收通道,数据可以同时向两个方向传输,PCIe spec称这种工作模式为双单工模式(dual-simplex),可以理解为全双工模式。

SATA的工作模式是什么?

和PCIE一样,SATA也有独立的发送和接收渠道,但不同于PCIE的工作模式:同时,只有一条路可以传输数据,也就是说,你在一条路上发送数据,在另一条路上无法接收数据,反之亦然。这种工作模式应该是半双工模式。PCIE就像我们的手机,双方都可以同时说话,而SATA就是对讲机,一个人在说话,另一个人只能听不能说。

回到前面的PCIE带宽表,上面的带宽,如PCIE3.0x1,带宽为2GB/s,是指双向带宽,即读写带宽。如果只是指读写,则该值应减半,即1GB/s的读写速度或写作速度。

让我们看看表中的带宽是如何计算出来的。

PCIE是串行总线,PCIE1.线上比特传输速率为2.5Gb/s,物理层使用8/10编码,即8比特数据,实际上需要在物理线路上传输10比特,因此:

PCIe1.0 x 带宽=(2.5)Gb/s x (双向通道)/ 10bit = 0.5GB/s

这是单个Lane的带宽,有几个Lane,那么整个带宽就是0.5GB/s乘以Lane的数量。

PCIe2.在PCIE1.0的基础上,0的在线比特传输速率翻了一番,为5Gb/s,物理层也使用8/10编码,因此:

PCIe2.0 x 1带宽=(5Gb/s x (双向通道)/ 10bit = 1GB/s

同样,有多少个Lane,带宽是1GB/s乘以Lane的数量。

PCIe3.在PCIE2.0的基础上,0的在线比特传输速率没有翻倍,也没有10Gb/s,而是8Gb/s,但物理层使用128/130编码进行数据传输,因此:

PCIe3.0 x 1带宽=(8Gb/s x (双向通道)/ 8bit = 2GB/s

同样,有多少Lane,带宽是2GB/s乘以Lane的数量。

由于128/130的编码和128比特的数据,只增加了2bit的成本,增加了有效数据传输的比例。虽然在线比特传输率没有翻倍,但在PCIE2.0的基础上,有效数据带宽翻了一番。

值得一提的是,上述数据带宽已经考虑到8/10或128/130的编码。因此,在计算带宽时,不需要考虑在线编码。

与SATA单通道不同,PCIE连接可以通过增加通道数来扩大带宽,充满弹性。通道越多,速度就越快。然而,渠道越多,成本就越高,占用的空间就越多,而且耗电量也就越大。因此,性能与其他因素之间应综合考虑使用多少通道。仅考虑性能,PCIE的最高带宽可达64GB/s,PCIe 3.0 x 32对应的带宽,一个非常可怕的数据。但是,现有的PCIE接口SSD,一般最多使用4个通道,如PCIE3.0x4,双向带宽为8GB/s,读或写带宽为4GB/s。

几个GB/s的传输速度,读写小电影那是杠杆。

顺便说一下,PCIE3.0x4理论上最大的4K IOPS。PCIe3.0x4理论最大读写速度为4GB/s,不管协议费用如何,每秒可以传输4GB/4K大小的IO,该值为1M,即理论上最大IOPS为1000K。所以,一个SSD,不管你底层用什么介质,flash还是3d, xpoint,接口速度就这样,最大IOPS是不可能超过这个值的。

PCIE是从PCI发展而来的,PCIE”e“是express的简称,快速的意思。PCIE如何比较PCI(或PCIE?-X)快呢?在物理传输方面,PCIE与PCI有本质的区别:PCI采用并口传输数据,而PCIE采用串口传输。我的PCI并行总线,一个时钟周期可以传输32bit或64bit,怎么能比不上一个时钟周期传输一个bit数据的串行总线呢?

在实际时钟频率相对较低的情况下,并口的速度确实比串口快,因为它可以同时传输几个比特。随着技术的发展,数据传输速率要求越来越快,时钟频率也越来越快,但并行总线的时钟频率并不快。

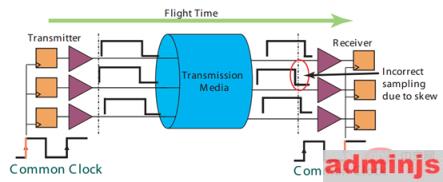

在发送端,数据沿某个时钟传输(左时钟的第一个上升边缘),在接收端接收下一个时钟边缘(右时钟的第二个上升边缘)。因此,为了在接收端正确收集数据,时钟周期必须大于数据传输时间(从发送端到接收端,flight time)。由于数据传输时间的限制(随着数据线长度的增加),时钟频率不能太高。此外,当时钟信号在线传输时,也会有相位偏移(clock skew ),影响接收端的数据采集;此外,并行传输,接收端必须等待最慢的bit数据到达后才能锁定整个数据 (signal skew)。

使用串行总线进行数据传输的PCIE没有这些问题。它没有外部时钟信号。它的时钟信息通过8/10或128/130嵌入到数据流中。接收器可以从数据流中恢复时钟信息。因此,它不受数据在线传输时间的限制。你的导线有多长没问题,你的数据传输频率有多快也没问题;没有外部时钟信号,自然就没有所谓的clock skew问题;由于是串行传输,只有一个bit传输,所以没有signal skew问题。但是,如果使用多个lane传输数据(串行中有并行,哈哈),这个问题又回来了,因为接收器要等到lane上最慢的数据到达才能处理整个数据。

PCIE总线基础知识

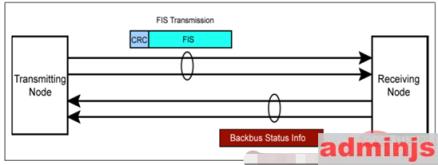

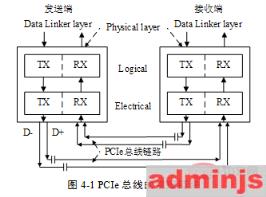

与PCI总线不同,PCIE总线采用端到端连接方式,一个设备只能在PCIE链路的两端连接一个设备,相互作为数据发送端和数据接收端。除了总线链路,PCIE总线还有多个层次。当发送端发送数据时,这些层次将通过这些层次使用,当接收端接收数据时,这些层次也将使用。PCIE总线使用的层次结构与网络协议栈相似。

PCIE链路采用“端到端数据传输模式”,TX(发送逻辑)和RX(接收逻辑)都包含在发送端和接收端,其结构如图所示。

如上图所示,PCIE总线物理链路中的一个数据通路(Lane)中,由两组差分信号组成,共4条信号线。其中,发送端的TX部件与接收端的RX部件连接一组差分信号,也称为发送端的发送链路和接收端的接收链路;发送端的RX部件与接收端的TX部件连接另一组差分信号,也称为发送端的接收链路和接收端的发送链路。一个PCIE链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串联一个电容器进行AC耦合。该电容器也被称为AC耦合电容器。PCIE链路使用差分信号进行数据传输,差分信号由D组成 与D-两个信号组成,信号接收器通过比较这两个信号的差异来判断发送器是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号具有更强的抗干扰能力,因为差分信号在接线时需要“等长”、“等宽”、“接近”,并在同一层。因此,外部干扰噪声将被“同值”和“同时”加载到D 理想情况下,与D-信号的差值为0,对信号的逻辑值影响不大。因此,差分信号可以使用更高的总线频率。

此外,使用差分信号可以有效抑制电磁干扰EMII(Electro Magnetic Interference)。由于信号D的差异 靠近D-,信号幅值相等,极性相反。这两条线与地线之间耦合电磁场的幅值相等,相互抵消,因此差分信号对外界的电磁干扰较小。当然,差分信号的缺点也很明显。一是差分信号用两个信号传输一个数据;二是差分信号的布线比较严格。

PCIE链路可由多个Lane组成,目前PCIE链路可支持1个、2、4、8、12、16和32个Lane,×1、×2、×4、×8、×12、×16和×32宽度的PCIE链路。每个Lane使用的总线频率与PCIE总线使用的版本有关。

第一个PCIE总线规范为V1.0,然后依次为V1.0a,V1.1,V2.0和V2.1。目前PCIE总线最新规范为V2.1,V3.0正在开发中,预计2010年发布。不同PCIE总线规范定义的总线频率和链路编码方法不同,如表41所示。

PCIE总线规范与总线频率与编码的关系

| PCIE总线规范 | 总线频率[1] | 单Lane峰值带宽 | 编码方式 |

|---|---|---|---|

| 1.x | 1.25GHz | 2.5GT/s | 8/10b编码 |

| 2.x | 2.5GHz | 5GT/s | 8/10b编码 |

| 3.0 | 4GHz | 8GT/s | 128/130b编码 |

如上表所示,不同PCIE总线规范使用的总线频率不同,使用的数据编码方法也不同。PCIE总线V1.x和V2.8/10b编码用于物理层,即PCIE链路上的10b编码 bit中含有8个 bit的有效数据;V3.0采用128/130b编码方法,即PCIE链路上的130b编码方法 bit中含有128 bit的有效数据。

如上表所示,V3.虽然0标准使用的总线频率只有4GHz,但其有效带宽为V2.x的两倍。下面将是V2。.以x规范为例,说明不同宽度PCIE链路所能提供的峰值带宽,如表42所示。

PCIE总线峰值带宽

| PCIE总线数据位宽 | ×1 | ×2 | ×4 | ×8 | ×12 | ×16 | ×32 |

|---|---|---|---|---|---|---|---|

| 峰值带宽(GT/s) | 5 | 10 | 20 | 40 | 60 | 80 | 160 |

由上表所示,×32PCIE链路可提供160GT/s链路带宽,远高于PCI/PCI-X总线所能提供的峰值带宽。以及即将到来的PCIee。 V3.规范使用4GHz的总线频率,将进一步提高PCIE链路的峰值带宽。

在PCIE总线中,使用GTIE(Gigatransfer)计算PCIE链路的峰值带宽。GT是在PCIE链路上传递的峰值带宽,其计算公式为总线频率×数据位宽×2。

在PCIE总线中,影响有效带宽的因素很多,因此很难计算出有效带宽。尽管如此,PCIE总线提供的有效带宽远高于PCI总线。PCIE总线也有其弱点,其中最突出的问题是传输延迟。

PCIE链路通过串行传输数据,但在芯片内部,数据总线仍然是平行的,因此PCIE链接接口需要串并转换,这将产生很大的延迟。此外,PCIE总线的数据报告需要通过事务层、数据链路层和物理层,这些数据报告在通过这些层次时也会带来延迟。

在基于PCIE总线的设备中,×1的PCIE链路是最常见的,×很少出现12个PCIE链路,×4和×8的PCIE设备也很少见。Intel通常集成在ICH中×1的PCIE链路用于连接低速外设,并在MCH中集成一个×用于连接显卡控制器的16个PCIE链路。PowerPC处理器通常可以支持×8、×4、×2和×1的PCIE链路。

PCIE总线物理链路之间的数据传输采用基于时钟的同步传输机制,但物理链路上没有时钟线。PCIE总线的接收端包含时钟恢复模块CDR(Clock Data Recovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传输。

值得注意的是,在PCIE设备中,除了从报文中提取时钟外,还使用REFCLK 与REFCLK-信号对作为本地参考时钟

更多相关知识,请访问常见问题栏目!

以上是pcie3.0x4最大速度的详细内容,更多请关注AdminJS的其他相关文章!